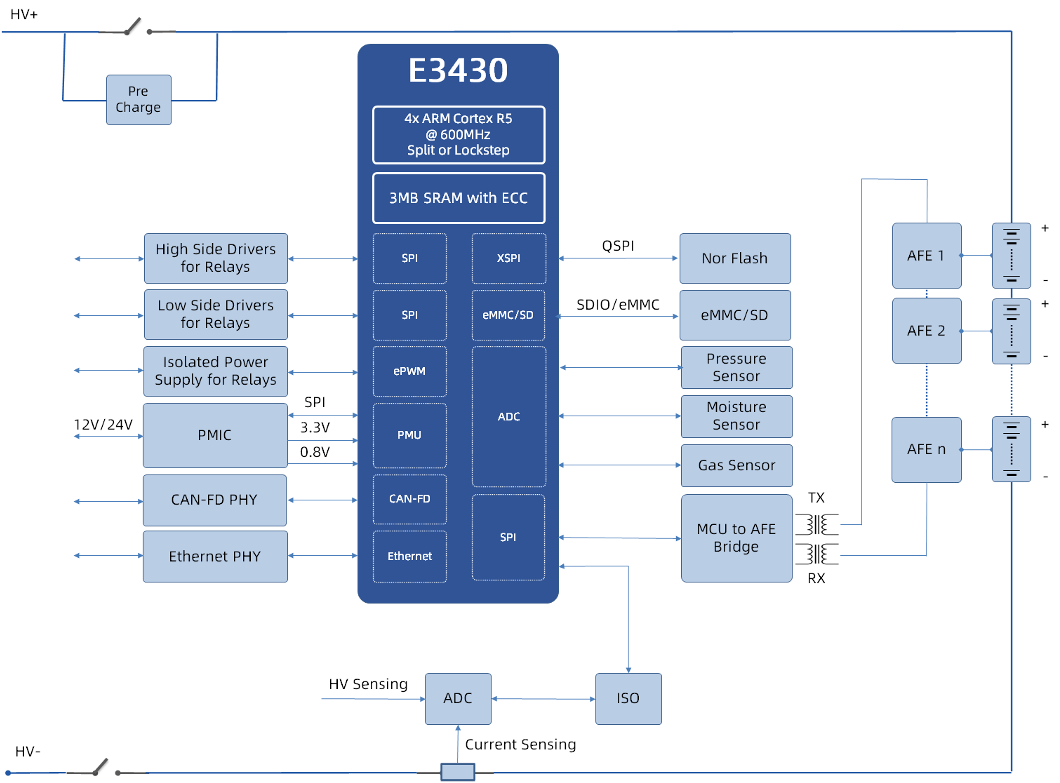

E3430具备两对双核锁步的ARM-Cortex R5 CPU Cluster,主频高达600MHz。其中CPU Cluster 1工作在Lock-Step模式,CPU Cluster 2可以由用户根据应用场景配置为Lock-Step模式或者Split模式。E3430最多可以提供3个独立运行的CPU并且都工作于600MHz的时钟频率,CPU算力高达3600DMIPS。

大容量片上存储:

3MB片上SRAM和384KB ECC SRAM,2对R5 CPU内核还分别配置了32KB I-Cache、32KB D-Cache,另有128KB的TCM存储器可以不经由总线以极低的延迟为CPU提供关键代码和数据,保障CPU性能的充分发挥。

丰富的外部存储扩展:

2个XSPI高速接口,用于支持包括Quad-SPI/Octal-SPI NOR FLASH、 HyperFLASH和HyperRAM,2个SEHC接口用于支持SD/SDIO和eMMC存储。

丰富的通信接口:

16个CAN-FD、 16个LIN、 2个支持TSN的千兆以太网和2个FlexRay,以及一个USB2.0接口。8个共支持32个SPI设备节点的SPI模块(使用模块片选信号)以及200个以上的可用I/O资源。这些丰富的外设资源有助于保障建立更多的管理和监控通道,应对不同电芯拓扑所带来的挑战。

模拟接口:

内置3个12-bit SARADC,4个Analog Comparator,支持单端和差分输入模式,共支持48路外部模拟信号接口。

采用BGA324封装,提供丰富I/O接口,每个数字I/O都具有GPIO功能且可以作为外部中断源输入。

功能安全等级支持ASIL D,采用双核锁步Cortex-R5,所有SRAM上都配置了错误检查和校正(ECC),在安全相关的外设上都配置了端到端(E2E)保护。

内置硬件信息安全模块,不仅支持经典公钥、哈希、对称加密和随机数生成算法,同时还支持国密商密SM2/3/4/9算法。

为了方便用户能够更快地了解E3430产品的特性,芯驰提供了基于E3430的BMS推荐方案。

E3430推荐方案应用优势

✓采用双核锁步CPU架构,具有多核、高主频的CPU设计;可以支撑当前及未来主流BMS对于算力和运算安全性的需求

✓集成丰富的通信及控制接口,丰富的I/O资源,不仅可以满足BMS应用需求,也支持对应用集成

✓可支持ASIL D级别功能安全系统设计,具有独立信息安全模块(HSM),支持国密商密相关算法

MCAL和SSDK软件包

在车规MCU领域,大部分用户都会采用AUTOSAR标准的软件包。芯驰针对E3430提供满足AUTOSAR标准的MCAL,实现微控制器、存储、通信和I/O等硬件的驱动程序,可以支持Vector、EB、普华、ETAS、东软睿驰、恒润(排名不分先后)等国内外主流AUTOSAR厂商的软件平台。为便于客户评估这些基本驱动模块,芯驰提供了AUTOSAR Demo程序,在设定的应用场景中展示这些基本模块的调用。

值得一提的是,为帮助客户顺利地运用E3430的各类安全机制,芯驰还提供基于AUTOSAR的功能安全软件库。用户可以参考功能安全手册,使用这些软件来完成最终的功能安全设计,实现各个功能模块的自检管理、故障应对、故障监控和事件记录。

此外,芯驰还为E3430 MCU开源提供基于FreeRTOS的SSDK软件包,主要包括操作系统、中间层和范例程序三个部分。

操作系统部分包含了FreeRTOS操作系统内核和适用于芯驰E3的BSP软件。BSP软件具体又囊括了CPU配置、系统模块配置、内外部存储驱动、各类外设和数模I/O驱动、外部器件驱动(以太网PHY、CAN收发器、LIN收发器、SBC等)和电源管理。

在中间层,芯驰提供了丰富的组件来满足不同客户的需求,如OTA服务、安全启动服务、信息安全服务、马达控制软件库、功能安全软件库、LWIP协议栈、Flash虚拟EEPROM等。

应用层软件部分,芯驰提供了丰富的范例程序,包括但不限于OTA升级、汽车以太网网关等。

在开发环境上,芯驰也已经可以支持IAR、Greenhills和GCC编译器,以及J-Link, LAUTERBACH等常用的调试器。